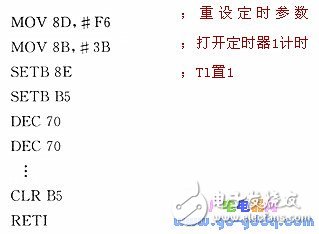

One of the key characteristics of dynamic memory is that it requires periodic refreshing because the stored data is volatile. In this system, the timer 1 interrupt of the 8031 microcontroller is utilized to perform the DRAM refresh operation. The following is the program code for the timer interrupt:

During the refresh process, Timer 1 is first configured. When the instruction "DEC 70H" is fetched from external program memory (EPROM), the PSEN signal becomes active. At this moment, the T1 pin goes high, which activates the RAS signal. Simultaneously, the address of the EPROM where the instruction is stored is also sent to the address bus. The lower 9 bits of this address are used as the row address for the DRAM, enabling the refresh of the memory row. Since the "DEC 70H" instruction operates on internal RAM, no other addresses appear on the address bus. By executing the "DEC 70H" instruction repeatedly (from 0200H to 0200H + 00FFH), the entire 1 MB DRAM can be refreshed, as it only needs a 9-bit row address.

Once the interrupt is triggered, the timer 1 parameters are immediately reset, and the timer is re-enabled to ensure continuous timing. The input clock for Timer 1 comes from the internal oscillator, with a count rate equal to 1/12 of the oscillator frequency. For example, if a 12 MHz crystal is used, the timer counts at 1 MHz. By setting the initial value to FFFFH, then F63BH, and finally 09C4H, the refresh interval is set to 2.5 ms. This is shorter than the standard 16 ms refresh cycle required by most 1 MB DRAMs, so the parameters could be adjusted to allow for longer intervals if needed.

Data Buffer Management

To manage the data buffer efficiently, a circular queue approach is implemented. The main program sends data to the host computer, while checking the head and tail pointers along with status flags to determine the buffer's state. An interrupt service routine receives incoming data and updates the DRAM accordingly. This method ensures that the buffer remains efficient and avoids data loss. It’s important that the DRAM refresh interrupt has a higher priority than the receive interrupt to guarantee timely memory refreshes and prevent data corruption.

Super Tweeter Bullet,Tweeter Driver,Speakers For Concert Speakers,Speakers For Performances

NINGBO RFUN AUDIO TECHNOLOGY CO.,LTD , https://www.mosensound.com