In recent years, data centers have increasingly adopted FPGAs as accelerators, with notable examples including Microsoft's Catapult, Amazon's Xilinx-based AWS F1, Intel's Altera, and Baidu. These data centers require massive parallel processing, high throughput, low latency, and energy efficiency. However, two major challenges remain: first, software-related issues such as efficient migration and performance guarantees for accelerated workloads; second, hardware challenges like managing many-core processors, 25–100G network interfaces, DRAM/HBM channels, and timing closure.

To address these challenges, the GRVI Phalanx FPGA accelerator framework has been introduced. GRVI stands for an FPGA-based RISC-V computing unit, specifically a RV321 soft processor core. Phalanx is a parallel FPGA accelerator framework that includes PE clusters, SRAM, accelerators, DRAM, and I/O control components, aiming to reduce the development and management costs of FPGA accelerators. It also incorporates Hoplite NoC, an FPGA-optimized directional 2D ring-on-chip network system that enables local memory sharing and global information exchange.

The GRVI Phalanx features a 1680-core computing unit based on a 32-bit RISC-V architecture. Each core is optimized by removing unnecessary resources, reducing chip area and improving efficiency. The design uses a three-stage pipeline with the RV321 core in user mode, and each unit requires 320 LUTs and operates at 375MHz. This design was implemented on a Xilinx UltraScale+ VU9P FPGA using the VCU118 Eval Kit. The chip contains 1680 manually placed units, each equipped with 8 RISC-V cores, 32–128 KB of RAM, and additional accelerators. It consumes 31–40W, with each core using only 24mW, achieving up to 0.4TIPS and 2.5TB/s memory bandwidth. Communication between cores and external I/O is handled via the Hoplite NoC, which supports 100 Gbps links between nodes.

The software side includes a multi-threaded C++ compiler, with hierarchical scheduling in the RV321MA GCC compiler. Future support for tools like OpenCL and P4 is planned. The GRVI Phalanx has also been deployed on the Zynq Z-7020 SOC for educational purposes on the PYNQ-Z1 board.

Moreover, hardware development is becoming more accessible through cloud platforms like Amazon AWS EC2 F1 instances, allowing developers to run their Verilog code without expensive hardware. This democratization of FPGA development is a game-changer for both research and industry.

In conclusion, data center accelerators must evolve in tandem with both software and hardware. Software needs to focus on portable, stable algorithms, while hardware can leverage multi-core solutions. Considerations such as software portability, tool usability, hardware complexity, and performance, power consumption, and maintainability are essential. Xilinx FPGAs continue to play a vital role in enabling high-performance parallel computing in data centers.

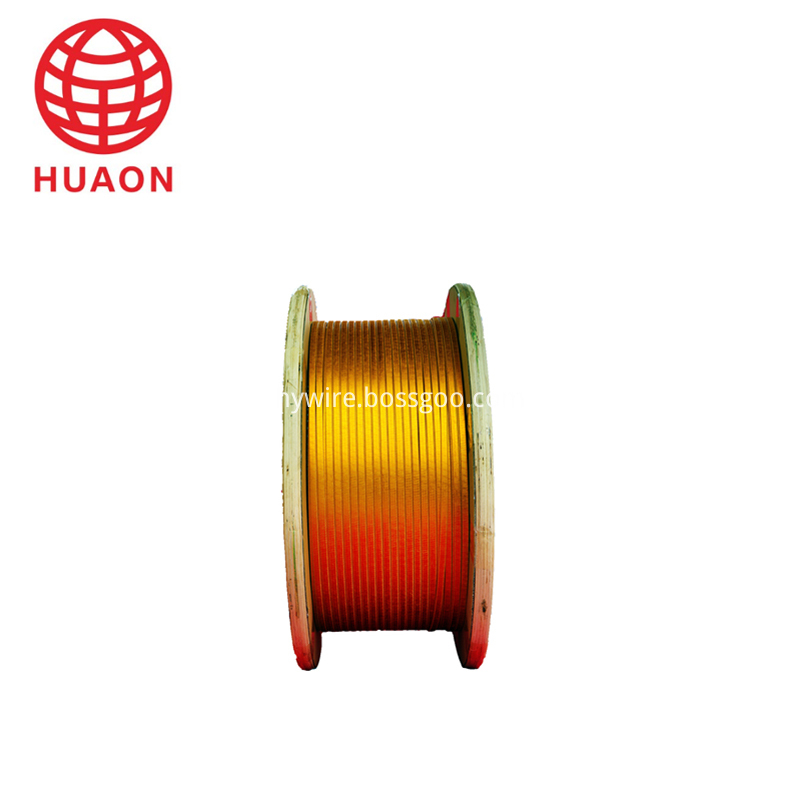

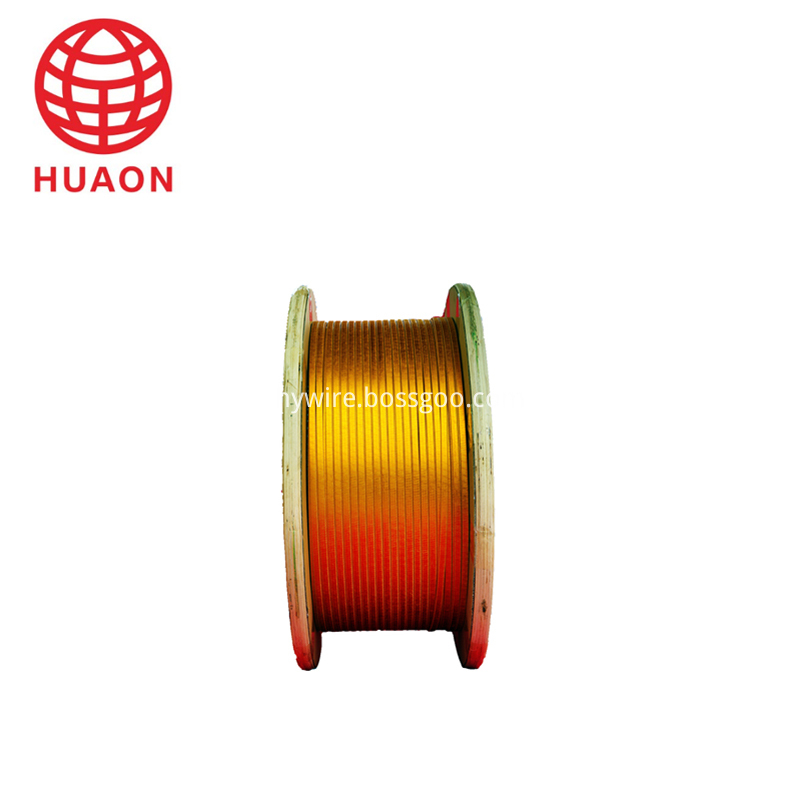

Film Overcoated With F46 Copper Flat Wire

|

About Film Overcoated With F46 Copper Flat Wire

|

Polyimide-F46 combined film wrapped sintered copper flat magnet wire insulation wire

This product provides high heat resistance, high cut through, solvent resistance, radiation resistance, cold resistance, freon resistance , etc .

The technical indexes for aluminium core enameled wire comply with enterprise standards extablished in reference to national standards .

Inner packing: in different wooden bobbin ,

Outer packing:wooden pallet with steel strip or according customers' special requirements

Film Wrapped Copper Wire,Film Overcoated With F46 Copper Flat Wire,F46 Copper Flat Wire,Film Covered With F46 Copper Flat Wire

HENAN HUAYANG ELECTRICAL TECHNOLOGY GROUP CO.,LTD , https://www.huaonwire.com