Verilog HDL is a hardware description language (HDL: Hardware DescripTIon Language), a language that describes the structure and behavior of digital system hardware in text form. It can represent logical circuit diagrams, logical expressions, and can also represent digital logic systems. Logic function. Verilog HDL and VHDL are the two most popular hardware description languages ​​in the world, all developed in the mid-1980s. The former was developed by Gateway Design AutomaTIon, which was acquired by Cadence in 1989. Both HDLs are IEEE standards.

Verilog was originally designed to be a hardware description language with a basic grammar similar to C. This is because the C language has been widely used in many fields at the beginning of Verilog design, and many language elements of C language have been used by many people. A hardware description language similar to C, which makes it easier for circuit designers to learn and accept. However, there are still many differences between Verilog and C. In addition, as a hardware description language different from ordinary computer programming languages, it also has some unique language elements, such as vector lines and registers in the form of vectors, non-blocking assignments in the process, and so on. In general, designers with C language will be able to quickly master the Verilog hardware description language.

C language is a general-purpose computer programming language that is widely used. The C language is designed to provide a programming language that can be easily compiled, processed with low-level memory, generated with a small amount of machine code, and run without any runtime environment support. Although the C language provides many low-level processing functions, it still maintains good cross-platform features. The C language program written in a standard specification can be compiled on many computer platforms, even including some embedded processors ( MCU) and supercomputer and other operating platforms. In the 1980s, in order to avoid differences in the C grammar used by developers, the National Bureau of Standards developed a complete set of international standard grammar for C, called ANSI C, as the initial standard for C.

Unique Features C is a procedural language with structured programming, variable scope, and recursive functionality. The C language passing parameters are passed by value, and a pointer passed by value. Different variable types can be combined together using structs. There are only 32 reserved keywords, which make variables and function names more flexible. Some variable types can be converted, such as integer and character variables. With the pointer, the C language can easily perform low-level control of the memory. The precompiler (preprocessor) makes the C language compilation more flexible.

The difference between Verilog language and C languageDigital circuit design engineers have generally learned the use of programming languages, digital logic foundations, and various EDA software tools. As far as programming languages ​​are concerned, most schools at home and abroad use the C language as the standard, and only a few schools use Pascal and Fortran.

The description and verification of the algorithm is usually done in C language. For example, to design a Reed-Solomen encoder/decoder, it can be divided into the following steps.

First understand the algorithm of Reed-Solomen encoding/decoding.

Write a C language program to verify the correctness of the algorithm.

The C language program describing the encoder is operated, and the plurality of sets of data to be encoded in the data file are converted into corresponding encoded data and stored in the file.

Write a C language program for interference, used to simulate channels. It can generate random error bits (and control the number of error bits within the error correction capability) and add it to the encoded data file. The interference program is run to generate an encoded data file with error bits.

Write a C language program for the decoder that runs the program to decode the encoded file with the error bit into another data file.

Comparing the original data file with the generated file, we can know whether the encoding and decoding procedures are correct (can automatically correct the error code bits within the error correction capability). In this way, we can verify the correctness of the algorithm. However, the speed of such data processing is only related to the size of the program and the running speed of the computer, and cannot exist independently of the computer.

If you want to design a special circuit to perform this real-time data processing that requires speed, in addition to the C program described above, you need to write a hardware description language (such as Verilog HDL or VHDL). Simulations are then performed to ensure that the algorithm is completed within the specified time from the circuit structure and that data can be exchanged correctly with the front-end and back-end devices or devices.

The advantages of programming hardware using hardware description language (HDL) are easy to understand, easy to maintain, fast debugging, many easy-to-follow simulation, synthesis, and place and route tools, and C language with HDL for logic design. Before and after simulation, verify that the function is correct.

In the development process of the algorithm hardware circuit, the structure of the calculation circuit and the process of the chip have a great influence on the operation speed. Therefore, multiple simulations must be performed before the circuit structure is determined.

Functional simulation of the C language.

Parallel structure simulation of C language.

Behavioral simulation of Verilog HDL.

Verilog HDL RTL level simulation.

Integrated backdoor level structure simulation.

Post-layout simulation.

The circuit is verified.

The following are three main issues to consider when designing the hardware circuit blocks of an algorithm in C language with Verilog HDL:

1. Why choose C for use with Verilog

First of all, C language is very flexible, and the debugging function is strong. You can also write your own system tasks through PLI (programming language interface) directly in combination with hardware emulators (such as Verilog-XL). C language is currently the most widely used programming language in the world, so the design environment of C program is more complete than Verilog HDL. In addition, the C language can be applied to many fields, has a reliable compilation environment, complete syntax, and fewer defects.

In comparison, the Verilog language is only described for hardware, and it is not convenient to use it elsewhere (eg for algorithmic expression, etc.). Moreover, most of Verilog's simulation, synthesis, and error-checking tools are commercial software. Compared with C language, it lacks long-term and large-scale use, and has poor reliability and many defects. Therefore, Verilog can only work better if it is used in conjunction with the C language.

In the face of the above problems, the best way is to use the C language and the Verilog language to complement each other. This is to use the integrity of the C language, combined with Verilog's accuracy of the hardware description, to quickly and better design the hardware circuit system to meet the performance requirements.

Using C's comprehensive troubleshooting and compilation environment, designers can design a functionally correct design unit as a standard for design comparison. Then, the C program is rewritten one by one into a C program described by a parallel structure (similar to Verilog). At this time, in the C environment, the C language is still used.

If the results are correct, replace the C language keyword with the corresponding Verilog keyword and enter the Verilog environment. Add the test input to both C and Verilog units and compare their outputs. This makes it easy to find out where the problem is, and then test it again until it is correct.

2. Problems in the conversion between C language and Verilog language

The mixed language design process often encounters many challenges in the conversion of the two languages, as shown below.

How to convert a C program into a C program like the Verilog structure.

How to increase the degree of parallelism to ensure that the running speed meets the design requirements when implemented in hardware.

How to not use the more abstract syntax in C (such as iterations, pointers, loops of indeterminate times, etc.). It is also possible to represent the algorithm (because the purpose of the conversion is to replace the statements in the C program with synthesizable Verilog statements, the Verilog syntax that can be used for synthesis is quite limited and often cannot be replaced by the corresponding keyword).

The C program is executed in order, and is a sequential structure. The hardware described by Verilog can be run at the same time and belongs to the parallel structure. There is a big conflict between the two. In addition, Verilog's simulation software is also executed sequentially, which is different from the actual hardware in terms of time, and there may be some problems that cannot be discovered.

The function call of C language is also different from the call of module in Verilog. C program calling function has no delay characteristics, a function is uniquely determined, and the same call to the same function is the same. Different calls to modules in Verilog are different, even if the same module is called, it must be specified with a different name.

Verilog's grammar rules are very dead, limited, and the available judgment statements are limited, the simulation speed is slow, the error detection function is poor, and the error information is incomplete. Simulation software is often expensive and not necessarily reliable. There are many tricks in the C language, and there are some difficulties in the conversion process.

There is no time relationship in C language. The converted Verilog program must be able to do without any additional artificial delay signals, otherwise the synthesis tool will not be able to convert Verilog source code into gate level logic.

3. How to use C language to speed up hardware design and troubleshooting

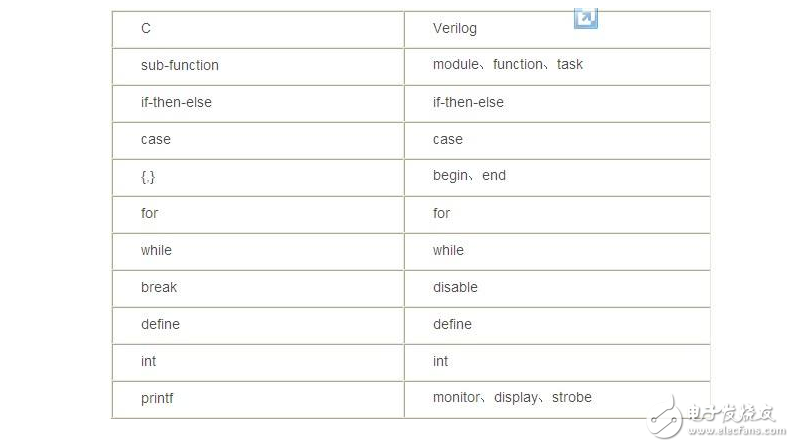

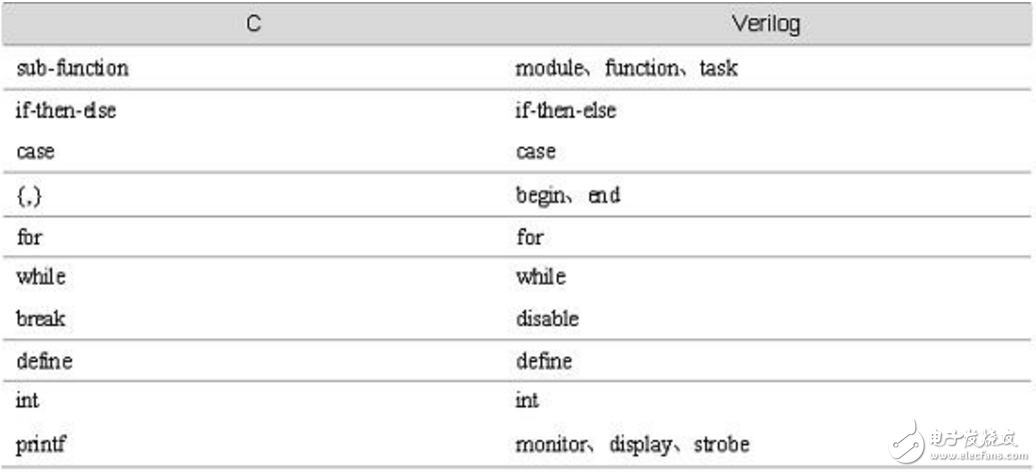

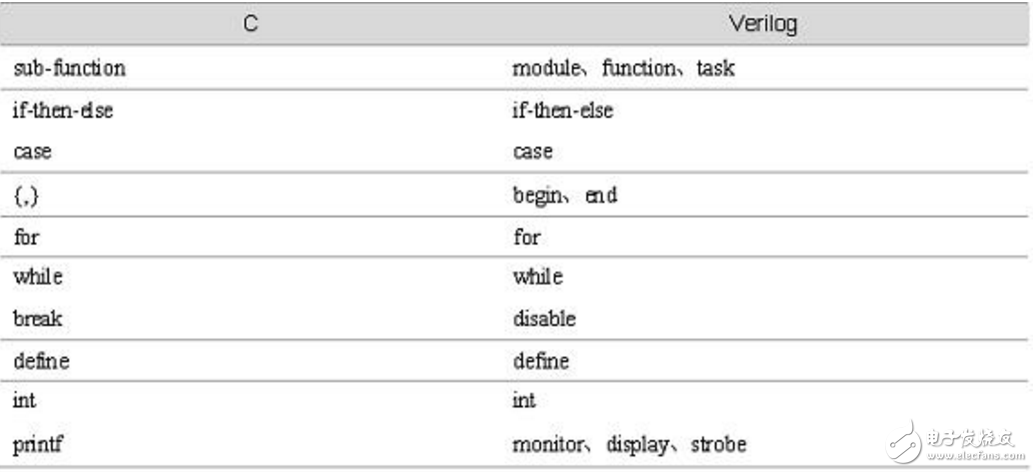

Table 3.11 shows the common keyword and control structure corresponding to Verilog in C language.

Table 3.11 Keyword and Control Structure Tables Corresponding to Verilog in C Language

The operator corresponding to the C language and Verilog is shown in Table 3.12.

Table 3.12 C language and Verilog correspondence operator table

From the above explanation we can summarize as follows.

C language and Verilog hardware description language can be used together to assist in designing hardware.

The C language is similar to the Verilog hardware description language, but with a few restrictions.

Programs in C are easily converted into Verilog programs.

Car Screen Protector,Car Center Console Screen Protector,Car Touchscreen Screen Protector

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.mct-sz.com